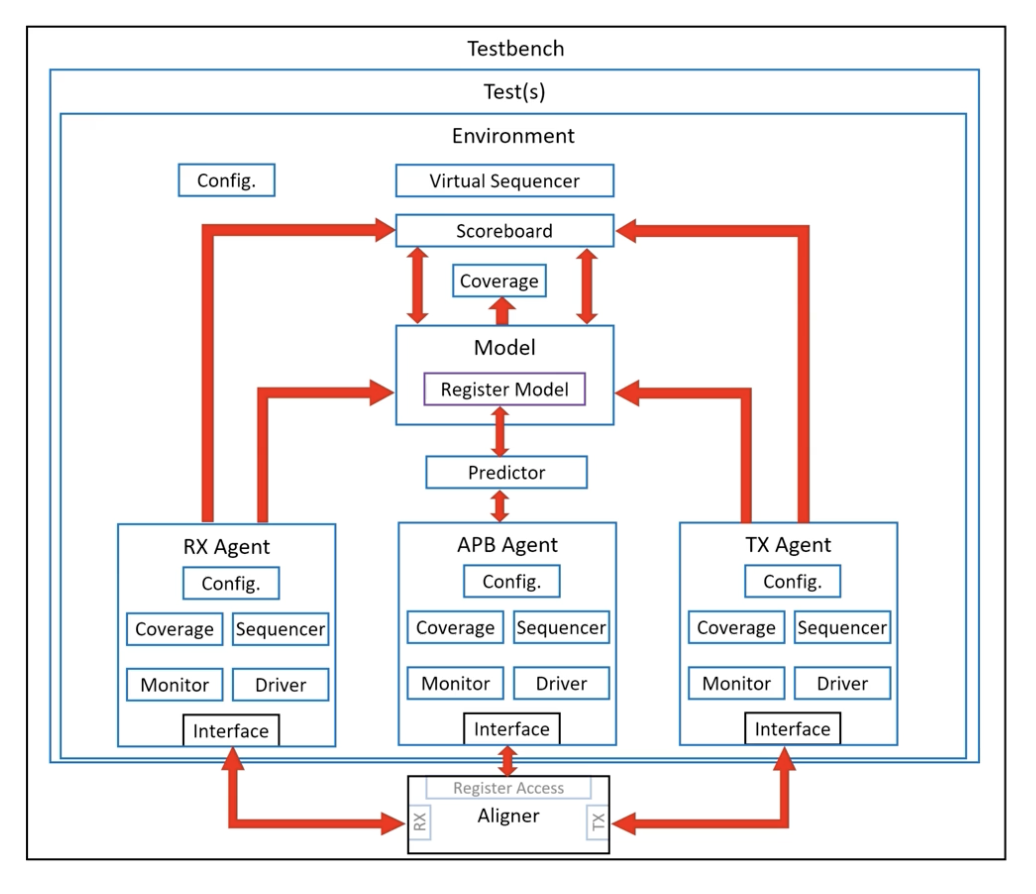

UVM Testbench Architecture

Overview

Developed a UVM testbench for a data alignment module. Utilized the UVM framework in SystemVerilog to design comprehensive test scenarios, ensuring robust and thorough verification of the module's functionality.

Details

- Created a reusable agent class to facilitate easy integration and testing of various modules.

- Implemented a model to simulate the expected behavior of the data alignment module.

- Developed a scoreboard to compare the module's output against the expected results, ensuring accuracy and reliability.

- Designed multiple test scenarios to cover a wide range of use cases and edge cases.

- Employed UVM's built-in features for reporting and logging, enhancing the debugging process.

- Ensured modularity and scalability of the testbench for future enhancements and adaptations.

Tools

- SystemVerilog

- UVM (Universal Verification Methodology)

- EDA Playground for simulation and testing